2024/04/30

2018/08/01

一般的なポールの話をするとまず出てくるであろう、ローパスフィルターの回路です。

ローパスフィルターは、周波数が低いときはそのまま出力して、周波数が高いときは出力を弱めていくようなフィルターです。

他にもフィルターとしては、ローパスの逆の動作をするハイパスフィルターや、特定の周波数から特定の周波数までを出力するバンドパスフィルター、バンドパスフィルターの逆の動作をするバンドエリミネーションフィルターなどがあります。

で、右側のグラフが、周波数に対して変化する利得と位相のグラフになっています。

周波数が低い時の利得は1(つまり入ってきた信号をそのまま出す)で、

周波数が高くなるにつれて20dB/decの傾きで落ちてってるのが分かると思います。

decっていう単位は周波数が10倍になったら、という単位です。

横軸が対数表記になっているので、そんな感じで表現しています。

この時の利得の落ち始めの周波数は100-200Hzの間になっているのが分かると思います。

この落ち始めの周波数のことをカットオフ周波数と呼び、ローパスフィルターのカットオフ周波数は1/2πRCで表現されます。

とはいえ、この落ち始めの定義は曖昧で、落ち始めってどこだよ?っていう疑問もあるので、正確には利得が-3dB(= 1/√2)になるところを落ち始めの点と定義しておきます。

この場合だと、R = 1kΩ、C = 1uFなので、1/2πRC = 159Hzとなります。

下のグラフは位相を表していて、入力に対して出力がどれだけ回転しているか?を表すグラフになります。

と言っても分からんので、別個で図を用意しました。

こんな感じです。

上のグラフが100Hzの時のもので、下のグラフが100kHzの時のものです。

上のグラフでは青線(入力)と緑線(出力)がほぼ同じようになっているのに対して、下のグラフでは上の入力と下の出力が微妙にずれているのが分かると思います。

ズレ具合としては、サイン波sin(t)とコサイン波-cos(t)程度ではないでしょうか?

つまり、sin(t)とsin(t - 90°)程度のズレがあるということです。

で、上の利得と位相のグラフに戻って欲しいのですが、100Hzのときは30°程度のズレに対して、100kHzのときは90°程度ズレております。

このようにローパスフィルターを噛ませると、カットオフ周波数よりもずっと高い周波数の信号の入力に対して出力が90°遅れる方にズレます。

この時のカットオフ周波数の点をポールと呼びます。

ポールの特徴としては以下のようなものがあります。

ポールにおける位相のズレ(遅れ)は45°

ポールにおける利得の減少は-3dB (カットオフ周波数なので)

ポール以降、周波数に対する利得は20dB/decで減少していく

ポールよりも十分に周波数の高い点では位相が90°遅れる方にズレる

ポールの位相に対する影響は、ポールの周波数/10くらいから現れはじめ、ポールの周波数 x10くらいで終わる

こんな感じです。

ポールを打ち消すような周波数の点をゼロと呼びます。

ゼロがあると利得が増えたり、位相は進む方に90°ズレたりします。

また、これらは伝達関数とかいう計算で表されるのですが、ポールを2点作ると利得の減少が40dB/decになったり、位相が180°ズレたりと、2倍の影響が出ます。

なので、利得が高い状態でポールが2点あると、そこから周波数に従って利得が落ち、また位相が180°ズレるので発振する可能性が高いです。

LTspice: Stability of Op Amp Circuits

とか見れば色々なところで紹介されていると思いますが、オペアンプのフィードバックをぶった切ってそこに周波数をスイープさせながら入力をぶち込んで出力を見ることで位相がどのくらい動き、利得がどのくらいで落ちるかなどがわかります。

これによって簡単にシミュレーションで発振するかしないかがわかります。

(これについてはまた別の機会に考察できればと思っていますが、今はそれを説明できる語彙力と理解力が無いので・・・)

上がシミュレーションした結果です。

2倍の非反転増幅回路を組んでいます。

また、オペアンプにはみんな大好きTL071を使っています。鉄板のオペアンプらしいですが、僕が生まれるずっとずっと前に出たやつです。

未だに手に入れられはするのですが、DIPパッケージが用意されているという特徴以外に今さら使う必然性は無いでしょう。もっと性能の良いオペアンプなら腐るほどある。

これを見ると、どうもポールは5MHzとかにあるっぽいですね。

しかも180°から0°に落ちているので、近いところにポールが2個あるようです。

この図では、0°が-180°ズレた、と受け取ってください。

つまり、位相が-180°回る前に利得がガッツリ落ちているので、この回路では問題なさげだということがわかります。

なお、シミュレーションにはLTSpiceや、TINA-TIあたりが無料で使えるやつです。

有料なものになると、PSpice一強でしょうか。

個人的にはTINA-TIを使っていますが、別に計算の精度や結果が変わるわけでもないので、何使っても良いと思います。

さて、ここで試しに出力に小さいキャパシタを挿入してみましょう。

ッ!?

なんかさっきと波形違うし。みたいなふうに思いましたか?

これはキャパシタが出力に付いたことでポールがどこかに一個付いてしまったみたいです。

位相のグラフを見てみれば分かると思いますが、さっきは高周波数帯では0°近辺でウロウロしていたのにもかかわらず、今回は-90°近辺でフラフラしています。

つまり、先程のグラフからさらにポールが一個増えてさらに-90°回ったということです。

出力にキャパシタを一個足したので、ポールができる条件の一つである、ローパスフィルターが形成されるまでには抵抗がもう一個必要です。

どこにあるんでしょうかね?

R2は今回のローパスフィルターの形成には関係ありません。電流はオペアンプ→キャパシタという順で流れていくので、オペアンプの内部回路の最終段あたりに抵抗があるはずのようです。

ここの解剖に関しては次以降に回します。

ともかく、小さいキャパシタを出力段に入れただけでずいぶんと変化してしました。

しかも悪いことに、位相が0°となる点(つまり-180°回る点)と利得が0dBになるところが重なりかけています。

これは発振する可能性が非常に高いです。

このように、小さいキャパシタが出力に付くだけで安定していた回路が一気に不安定になることがあるので注意してください。

また、キャパシタは意外と寄生容量となって線間に潜んでいたりするので、素子を載せていなくても、レイアウトやパターンだけで発振することもあるので、そのあたりも加味して設計なり開発なりをする必要があります。

今日は書くのに疲れたので、このあたりで筆(キーボード)を置くことにします。

次あたりでオペアンプの中身やなぜ出力段に抵抗が形成されたりするのか〜みたいなところについてやっていければと思いますが、そこまで頭良くない(泣)

[PR]

×

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

コメント

ただいまコメントを受けつけておりません。

【備忘録】オペアンプの発振条件について考察してみた 2

今回はシミュレーションとかを活用しながらポールとかそっち方面を攻めてみようと思います。

1. ポールについて

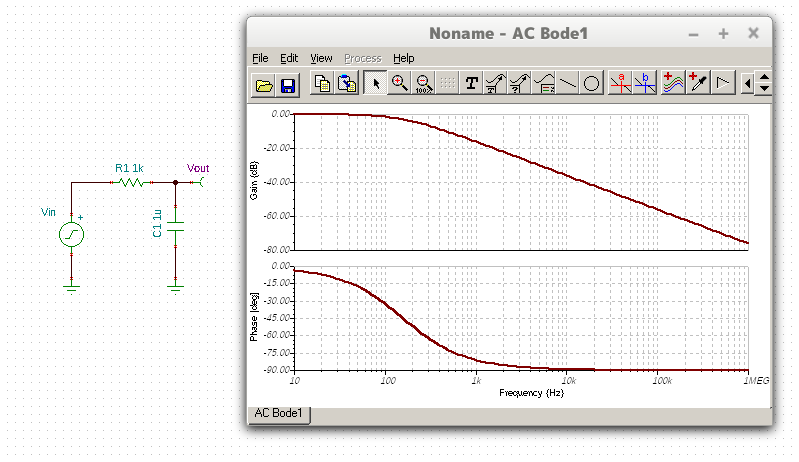

まず、下の図を見てほしいです。一般的なポールの話をするとまず出てくるであろう、ローパスフィルターの回路です。

ローパスフィルターは、周波数が低いときはそのまま出力して、周波数が高いときは出力を弱めていくようなフィルターです。

他にもフィルターとしては、ローパスの逆の動作をするハイパスフィルターや、特定の周波数から特定の周波数までを出力するバンドパスフィルター、バンドパスフィルターの逆の動作をするバンドエリミネーションフィルターなどがあります。

で、右側のグラフが、周波数に対して変化する利得と位相のグラフになっています。

周波数が低い時の利得は1(つまり入ってきた信号をそのまま出す)で、

周波数が高くなるにつれて20dB/decの傾きで落ちてってるのが分かると思います。

decっていう単位は周波数が10倍になったら、という単位です。

横軸が対数表記になっているので、そんな感じで表現しています。

この時の利得の落ち始めの周波数は100-200Hzの間になっているのが分かると思います。

この落ち始めの周波数のことをカットオフ周波数と呼び、ローパスフィルターのカットオフ周波数は1/2πRCで表現されます。

とはいえ、この落ち始めの定義は曖昧で、落ち始めってどこだよ?っていう疑問もあるので、正確には利得が-3dB(= 1/√2)になるところを落ち始めの点と定義しておきます。

この場合だと、R = 1kΩ、C = 1uFなので、1/2πRC = 159Hzとなります。

下のグラフは位相を表していて、入力に対して出力がどれだけ回転しているか?を表すグラフになります。

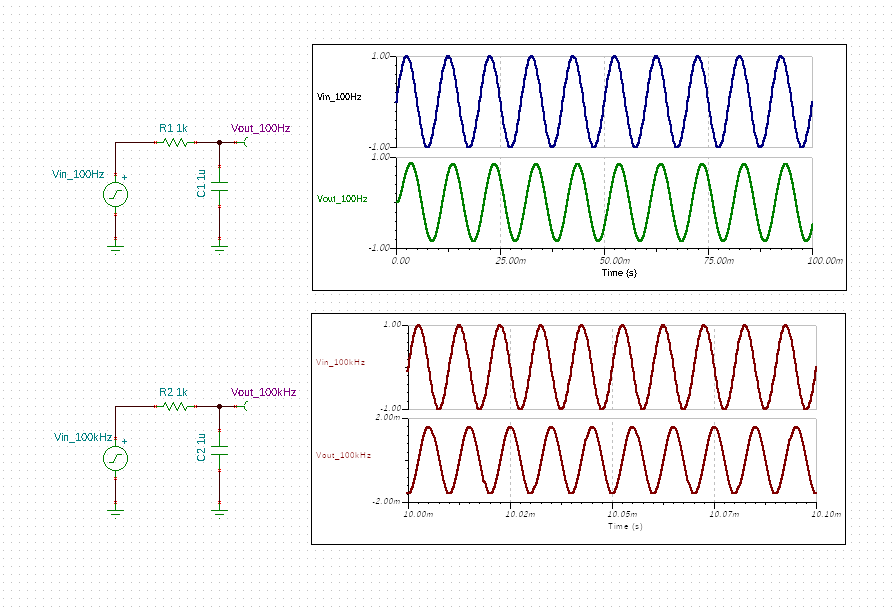

と言っても分からんので、別個で図を用意しました。

こんな感じです。

上のグラフが100Hzの時のもので、下のグラフが100kHzの時のものです。

上のグラフでは青線(入力)と緑線(出力)がほぼ同じようになっているのに対して、下のグラフでは上の入力と下の出力が微妙にずれているのが分かると思います。

ズレ具合としては、サイン波sin(t)とコサイン波-cos(t)程度ではないでしょうか?

つまり、sin(t)とsin(t - 90°)程度のズレがあるということです。

で、上の利得と位相のグラフに戻って欲しいのですが、100Hzのときは30°程度のズレに対して、100kHzのときは90°程度ズレております。

このようにローパスフィルターを噛ませると、カットオフ周波数よりもずっと高い周波数の信号の入力に対して出力が90°遅れる方にズレます。

この時のカットオフ周波数の点をポールと呼びます。

ポールの特徴としては以下のようなものがあります。

ポールにおける位相のズレ(遅れ)は45°

ポールにおける利得の減少は-3dB (カットオフ周波数なので)

ポール以降、周波数に対する利得は20dB/decで減少していく

ポールよりも十分に周波数の高い点では位相が90°遅れる方にズレる

ポールの位相に対する影響は、ポールの周波数/10くらいから現れはじめ、ポールの周波数 x10くらいで終わる

こんな感じです。

ポールを打ち消すような周波数の点をゼロと呼びます。

ゼロがあると利得が増えたり、位相は進む方に90°ズレたりします。

また、これらは伝達関数とかいう計算で表されるのですが、ポールを2点作ると利得の減少が40dB/decになったり、位相が180°ズレたりと、2倍の影響が出ます。

なので、利得が高い状態でポールが2点あると、そこから周波数に従って利得が落ち、また位相が180°ズレるので発振する可能性が高いです。

2. オペアンプの発振について

さて、次はオペアンプにこのポールやらゼロやらを適用してみます。LTspice: Stability of Op Amp Circuits

とか見れば色々なところで紹介されていると思いますが、オペアンプのフィードバックをぶった切ってそこに周波数をスイープさせながら入力をぶち込んで出力を見ることで位相がどのくらい動き、利得がどのくらいで落ちるかなどがわかります。

これによって簡単にシミュレーションで発振するかしないかがわかります。

(これについてはまた別の機会に考察できればと思っていますが、今はそれを説明できる語彙力と理解力が無いので・・・)

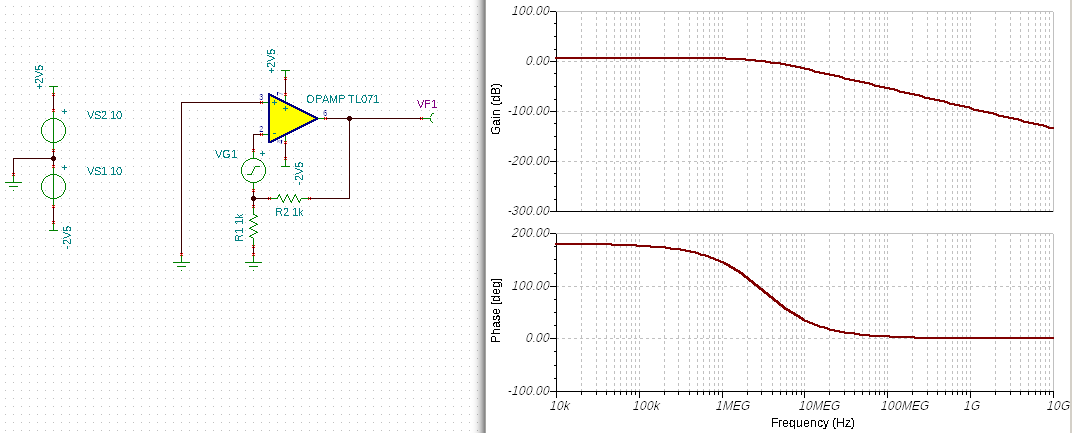

上がシミュレーションした結果です。

2倍の非反転増幅回路を組んでいます。

また、オペアンプにはみんな大好きTL071を使っています。鉄板のオペアンプらしいですが、僕が生まれるずっとずっと前に出たやつです。

未だに手に入れられはするのですが、DIPパッケージが用意されているという特徴以外に今さら使う必然性は無いでしょう。もっと性能の良いオペアンプなら腐るほどある。

これを見ると、どうもポールは5MHzとかにあるっぽいですね。

しかも180°から0°に落ちているので、近いところにポールが2個あるようです。

この図では、0°が-180°ズレた、と受け取ってください。

つまり、位相が-180°回る前に利得がガッツリ落ちているので、この回路では問題なさげだということがわかります。

なお、シミュレーションにはLTSpiceや、TINA-TIあたりが無料で使えるやつです。

有料なものになると、PSpice一強でしょうか。

個人的にはTINA-TIを使っていますが、別に計算の精度や結果が変わるわけでもないので、何使っても良いと思います。

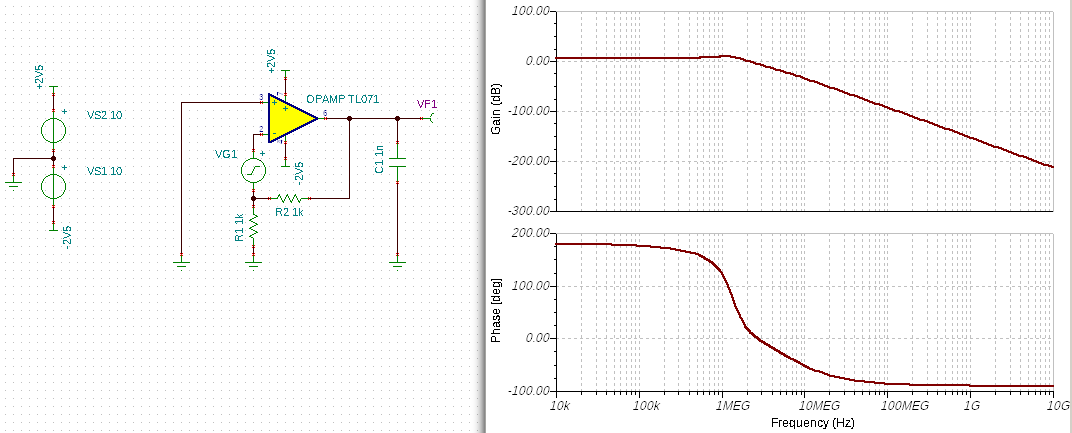

さて、ここで試しに出力に小さいキャパシタを挿入してみましょう。

ッ!?

なんかさっきと波形違うし。みたいなふうに思いましたか?

これはキャパシタが出力に付いたことでポールがどこかに一個付いてしまったみたいです。

位相のグラフを見てみれば分かると思いますが、さっきは高周波数帯では0°近辺でウロウロしていたのにもかかわらず、今回は-90°近辺でフラフラしています。

つまり、先程のグラフからさらにポールが一個増えてさらに-90°回ったということです。

出力にキャパシタを一個足したので、ポールができる条件の一つである、ローパスフィルターが形成されるまでには抵抗がもう一個必要です。

どこにあるんでしょうかね?

R2は今回のローパスフィルターの形成には関係ありません。電流はオペアンプ→キャパシタという順で流れていくので、オペアンプの内部回路の最終段あたりに抵抗があるはずのようです。

ここの解剖に関しては次以降に回します。

ともかく、小さいキャパシタを出力段に入れただけでずいぶんと変化してしました。

しかも悪いことに、位相が0°となる点(つまり-180°回る点)と利得が0dBになるところが重なりかけています。

これは発振する可能性が非常に高いです。

このように、小さいキャパシタが出力に付くだけで安定していた回路が一気に不安定になることがあるので注意してください。

また、キャパシタは意外と寄生容量となって線間に潜んでいたりするので、素子を載せていなくても、レイアウトやパターンだけで発振することもあるので、そのあたりも加味して設計なり開発なりをする必要があります。

今日は書くのに疲れたので、このあたりで筆(キーボード)を置くことにします。

次あたりでオペアンプの中身やなぜ出力段に抵抗が形成されたりするのか〜みたいなところについてやっていければと思いますが、そこまで頭良くない(泣)

コメント

カテゴリー

最新記事

(08/19)

(07/16)

(06/11)

(06/06)

(06/05)

カレンダー

アーカイブ

AD

PR